# Synchronous PWM Switching Converter

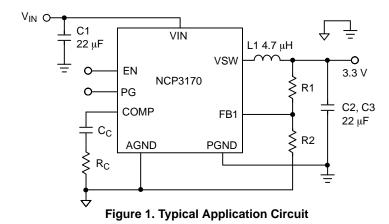

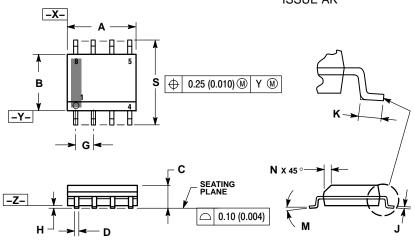

The NCP3170 is a flexible synchronous PWM Switching Buck Regulator. The NCP3170 operates from 4.5 V to 18 V, sourcing up to 3 A and is capable of producing output voltages as low as 0.8 V. The NCP3170 also incorporates current mode control. To reduce the number of external components, a number of features are internally set including soft start, power good detection, and switching frequency. The NCP3170 is currently available in an SOIC–8 package.

#### **Features**

- 4.5 V to 18 V Operating Input Voltage Range

- 90 m $\Omega$  High-Side, 25 m $\Omega$  Low-Side Switch

- FMEA Fault Tolerant During Pin Short Test

- 3 A Continuous Output Current

- Fixed 500 kHz and 1 MHz PWM Operation

- Cycle-by-Cycle Current Monitoring

- 1.5% Initial Output Accuracy

- Internal 4.6 ms Soft-Start

- Short-Circuit Protection

- Turn on Into Pre-bias

- Power Good Indication

- Light Load Efficiency

- Thermal Shutdown

- These are Pb-Free Devices

# **Typical Applications**

- Set Top Boxes

- DVD/Blu–ray<sup>™</sup> Drives and HDD

- LCD Monitors and TVs

- Cable Modems

- PCIe Graphics Cards

- Telecom/Networking/Datacom Equipment

- Point of Load DC/DC Converters

# ON Semiconductor®

http://onsemi.com

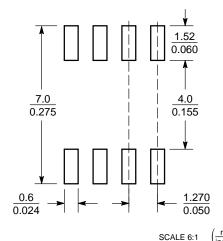

SOIC-8 NB CASE 751

# MARKING DIAGRAM

3170x = Specific Device Code

x = A or B

A = Assembly Location

L = Wafer Lot Y = Year

W = Work Week

■ Pb-Free Package

#### **PIN CONNECTIONS**

# **ORDERING INFORMATION**

| Device       | Package             | Shipping <sup>†</sup> |

|--------------|---------------------|-----------------------|

| NCP3170ADR2G | SOIC-8<br>(Pb-Free) | 2,500/Tape & Reel     |

| NCP3170BDR2G | SOIC-8<br>(Pb-Free) | 2,500/Tape & Reel     |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

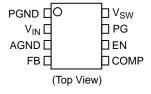

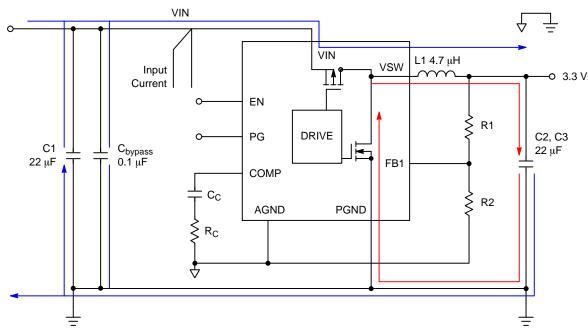

Figure 2. NCP3170 Block Diagram

# **Table 1. PIN FUNCTION DESCRIPTION**

| Pin | Pin Name | Description                                                                                                                                                                                                                                                                                                 |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | PGND     | The power ground pin is the high current path for the device. The pin should be soldered to a large copper area to reduce thermal resistance. PGND needs to be electrically connected to AGND.                                                                                                              |

| 2   | VIN      | The input voltage pin powers the internal control circuitry and is monitored by multiple voltage comparators. The VIN pin is also connected to the internal power PMOS switch and linear regulator output. The VIN pin has high di/dt edges and must be decoupled to ground close to the pin of the device. |

| 3   | AGND     | The analog ground pin serves as small-signal ground. All small-signal ground paths should connect to the AGND pin and should also be electrically connected to power ground at a single point, avoiding any high current ground returns.                                                                    |

| 4   | FB       | Inverting input to the OTA error amplifier. The FB pin in conjunction with the external compensation serves to stabilize and achieve the desired output voltage with current mode compensation.                                                                                                             |

| 5   | COMP     | The loop compensation pin is used to compensate the transconductance amplifier which stabilizes the operation of the converter stage. Place compensation components as close to the converter as possible. Connect a RC network between COMP and AGND to compensate the control loop.                       |

| 6   | EN       | Enable pin. Pull EN to logic high to enable the device. Pull EN to logic low to disable the device. Do not leave it open.                                                                                                                                                                                   |

| 7   | PG       | Power good is an open drain 500 $\mu$ A pull down indicating output voltage is within the power good window. If the power good function is not used, it can be connected to the VSW node to reduce thermal resistance. Do not connect PG to the VSW node if the application is turning on into pre-bias.    |

| 8   | VSW      | The VSW pin is the connection of the drains of the internal N and P MOSFETS. At switch off, the inductor will drive this pin below ground as the body diode and the NMOS conducts with a high dv/dt.                                                                                                        |

Table 2. ABSOLUTE MAXIMUM RATINGS (measured vs. GND pin 3, unless otherwise noted)

| Rating                                                                                                                                                                           | Symbol                     | V <sub>MAX</sub>        | V <sub>MIN</sub>  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------|-------------------|------|

| Main Supply Voltage Input                                                                                                                                                        | V <sub>IN</sub>            | 20                      | -0.3              | V    |

| Voltage between PGND and AGND                                                                                                                                                    | V <sub>PAG</sub>           | 0.3                     | -0.3              | V    |

| PWM Feedback Voltage                                                                                                                                                             | F <sub>B</sub>             | 6                       | -0.3              | V    |

| Error Amplifier Voltage                                                                                                                                                          | COMP                       | 6                       | -0.3              | V    |

| Enable Voltage                                                                                                                                                                   | EN                         | V <sub>IN</sub> + 0.3 V | -0.3              | V    |

| PG Voltage                                                                                                                                                                       | PG                         | V <sub>IN</sub> + 0.3 V | -0.3              | V    |

| VSW to AGND or PGND                                                                                                                                                              | V <sub>SW</sub>            | V <sub>IN</sub> + 0.3 V | -0.7              | V    |

| VSW to AGND or PGND for 35ns                                                                                                                                                     | V <sub>SWST</sub>          | V <sub>IN</sub> + 10 V  | -5                | V    |

| Junction Temperature (Note 1)                                                                                                                                                    | T <sub>J</sub>             | +1                      | °C                |      |

| Operating Ambient Temperature Range                                                                                                                                              | T <sub>A</sub>             | -40 to                  | o +85             | °C   |

| Storage Temperature Range                                                                                                                                                        | T <sub>stg</sub>           | – 55 to                 | °C                |      |

| Thermal Characteristics (Note 2) SOIC–8 Plastic Package Maximum Power Dissipation @ T <sub>A</sub> = 25°C Thermal Resistance Junction-to-Air Thermal Resistance Junction-to-Case | 1. <sup>°</sup><br>8<br>37 | 7                       | W<br>°C/W<br>°C/W |      |

| Lead Temperature Soldering (10 sec):<br>Reflow (SMD Styles Only) Pb-Free (Note 3)                                                                                                | RF                         | 260 peak °C             |                   |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

The maximum package power dissipation limit must not be exceeded.

$$P_D = \frac{T_{J(max)} - T_A}{R_{\theta JA}}$$

- 2. The value of  $\theta$ JA is measured with the device mounted on 2in x 2in FR-4 board with 2oz. copper, in a still air environment with  $T_A = 25^{\circ}$ C. The value in any given application depends on the user's specific board design.

- 3. 60-180 seconds minimum above 237°C.

**Table 3. RECOMMENDED OPERATING CONDITIONS**

| Rating                      | Symbol          | Min  | Max  | Unit |

|-----------------------------|-----------------|------|------|------|

| Main Supply Voltage Input   |                 | 4.5  | 18   | V    |

| Power Good Pin Voltage      | PG              | 4.5  | 18   | V    |

| Switch Pin Voltage          | V <sub>SW</sub> | -0.3 | 18   | V    |

| Enable Pin Voltage          | EN              | 0    | 18   | V    |

| Comp Pin Voltage            | COMP            | -0.1 | 5.5  | V    |

| Feedback Pin Voltage        | FB              | -0.1 | 5.5  | V    |

| Power Ground Pin Voltage    | PGND            | -0.1 | -0.1 | V    |

| Junction Temperature Range  | TJ              | -40  | 125  | °C   |

| Operating Temperature Range | T <sub>A</sub>  | -40  | 85   | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

**Table 4. ELECTRICAL CHARACTERISTICS**

$(T_A = 25^{\circ}C, V_{IN} = V_{EN} = 12 \text{ V}, V_{OUT} = 3.3 \text{ V} \text{ for min/max values unless otherwise noted (Note 7))}$

| Characteristic                                 |                      | Conditions                                                      | Min         | Тур         | Max         | Unit   |

|------------------------------------------------|----------------------|-----------------------------------------------------------------|-------------|-------------|-------------|--------|

| Input Voltage Range                            | (Note 5)             | 4.5                                                             | _           | 18          | V           |        |

| SUPPLY CURRENT                                 | <u>.</u>             |                                                                 |             |             |             |        |

| Quiescent Supply Current                       | NCP3170A<br>NCP3170B | V <sub>IN</sub> = EN = 12 V V <sub>FB</sub> = 0.8 V<br>(Note 5) | -           | 1.7<br>1.7  | 2.0<br>2.0  | mA     |

| Shutdown Supply Current                        |                      | EN = 0 V (Note 5)                                               | -           | 13          | 17          | μΑ     |

| UNDER VOLTAGE LOCKOUT                          |                      |                                                                 | •           | •           | •           | •      |

| VIN UVLO Threshold                             |                      | V <sub>IN</sub> Rising Edge (Note 5)                            | -           | 4.41        | _           | V      |

| VIN UVLO Threshold                             |                      | V <sub>IN</sub> Falling Edge (Note 5)                           | _           | 4.13        | _           | V      |

| MODULATOR                                      |                      |                                                                 |             |             |             |        |

| Oscillator Frequency                           | NCP3170A<br>NCP3170B | Enable = V <sub>IN</sub>                                        | 450<br>900  | 500<br>1000 | 550<br>1100 | kHz    |

| Maximum Duty Ratio                             | NCP3170A<br>NCP3170B |                                                                 | 91<br>90    | _<br>_      | 96<br>96    | %      |

| Minimum Duty Ratio                             | NCP3170A<br>NCP3170B | V <sub>IN</sub> = 12 V                                          | 6.0<br>4.0  | _<br>_      | 11<br>11.5  | %      |

| VIN Soft Start Ramp Time                       |                      | $V_{FB} = VCOMP$                                                | 3.5         | 4.6         | 6.0         | ms     |

| OVER CURRENT                                   | <b>·</b>             |                                                                 |             |             |             |        |

| Current Limit                                  |                      | (Note 4)                                                        | 4.0         | -           | 6.0         | Α      |

| PWM COMPENSATION                               |                      |                                                                 |             |             |             |        |

| VFB Feedback Voltage                           |                      | T <sub>A</sub> = 25°C                                           | 0.792       | 0.8         | 0.808       | V      |

| Line Regulation                                |                      | (Note 4)                                                        | _           | 1           | _           | %      |

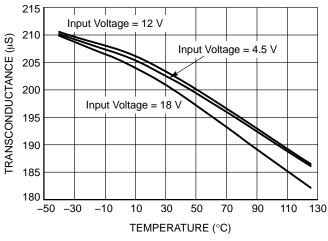

| GM                                             |                      |                                                                 | -           | 201         | -           | μS     |

| AOL DC gain                                    |                      | (Note 4)                                                        | 40          | 55          | _           | dB     |

| Unity Gain BW (C <sub>OUT</sub> = 10 pF)       |                      | (Note 4)                                                        | 2.0         | _           | _           | MHz    |

| Input Bias Current (Current Out of FB IB Pin)  |                      | (Note 4)                                                        | _           | _           | 286         | nA     |

| IEAOP Output Source Current                    |                      | $V_{FB} = 0 V$                                                  | _           | 20.1        | _           | μΑ     |

| IEAOM Output Sink Current                      |                      | $V_{FB} = 2 V$                                                  | _           | 21.3        | _           | μΑ     |

| ENABLE                                         |                      |                                                                 |             |             |             |        |

| Enable Threshold                               |                      | (Note 5)                                                        | _           | 1.41        | _           | V      |

| POWER GOOD                                     |                      |                                                                 |             |             |             |        |

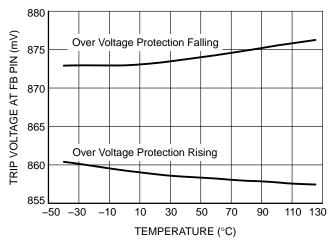

| Power Good High On Threshold                   |                      |                                                                 | _           | 875         | _           | mV     |

| Power Good High Off Threshold                  |                      |                                                                 | -           | 859         | _           | mV     |

| Power Good Low On Threshold                    |                      |                                                                 | _           | 712         | _           | mV     |

| Power Good Low Off Threshold                   |                      |                                                                 | _           | 728         | _           | mV     |

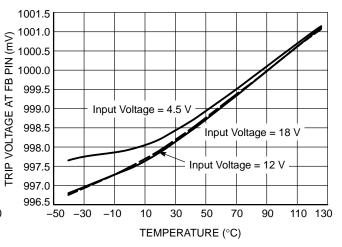

| Over Voltage Protection Threshold              |                      |                                                                 | _           | 998         | _           | mV     |

| Power Good Low Voltage                         |                      | $V_{IN}$ = 12 V, IPG = 500 $\mu A$                              | _           | 0.195       | _           | V      |

| PWM OUTPUT STAGE                               |                      |                                                                 |             |             |             |        |

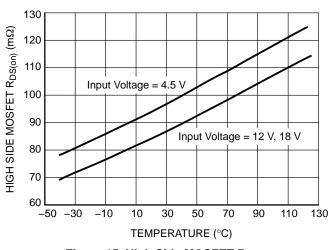

| High-Side Switch On-Resistance                 |                      | $V_{IN} = 12 V$<br>$V_{IN} = 4.5 V$                             | 1 1         | 90<br>100   | 130<br>150  | mΩ     |

| Low-Side Switch On-Resistance                  |                      | $V_{IN} = 12 V$<br>$V_{IN} = 4.5 V$                             |             | 25<br>29    | 35<br>39    | mΩ     |

| THERMAL SHUTDOWN                               |                      |                                                                 |             |             |             |        |

| Thermal Shutdown                               |                      | (Notes 4 and 6)                                                 | _           | 164         | _           | °C     |

| Hysteresis                                     |                      |                                                                 | -           | 43          | _           | °C     |

| Product parametric performance is indicated in | n the Electrical (   | Characteristics for the listed test co                          | nditions ur | nless other | rwise note  | d Prod |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

4. Guaranteed by design

- 5. Ambient temperature range of -40°C to +85°C.6. This is not a protection feature.

- 7. The device is not guaranteed to operate beyond the maximum operating ratings.

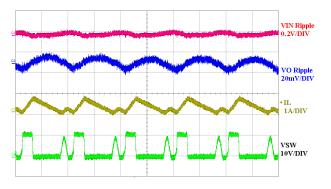

# TYPICAL PERFORMANCE CHARACTERISTICS

(Circuit from Figure 1,  $T_A = 25$ °C,  $V_{IN} = V_{EN} = 12$  V,  $V_{OUT} = 3.3$  V unless otherwise specified)

VIN Ripple

0.2V/DIV

VO Ripple

20mV/DIV

IL

1A/DIV

VSW

10V/DIV

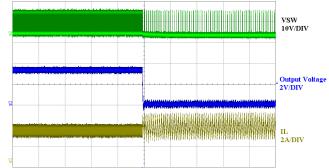

Figure 3. Light Load (DCM) Operation 1 µs/DIV

Figure 4. Full Load (CCM) Operation 1 μs/DIV

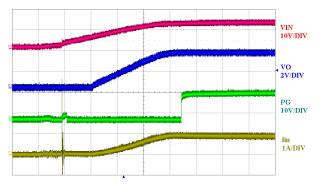

Figure 5. Start-Up into Full Load 1 ms/DIV

Figure 6. Short–Circuit Protection 200  $\mu s$  /DIV

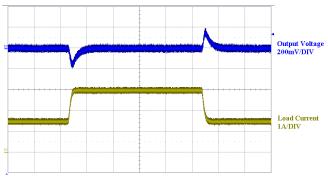

Figure 7. 50% to 100% Load Transient 100 μs/DIV

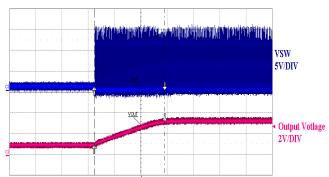

Figure 8. 3.3 V Turn on into 1 V Pre-Bias 1 ms /DIV

### TYPICAL PERFORMANCE CHARACTERISTICS

(Circuit from Figure 1,  $T_A = 25$ °C,  $V_{IN} = V_{EN} = 12$  V,  $V_{OUT} = 3.3$  V unless otherwise specified)

Input Voltage = 18 V 2.0 CURRENT DRAW (mA) Input Voltage = 12 V 1.9 1.8 1.7 1.6 Input Voltage = 4.5 V 1.5 1.4 1.3 30 50 70 110 130 -50 -3090 TEMPERATURE (°C)

Figure 9. ICC Shut Down Current vs.

Temperature

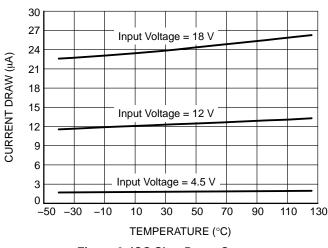

Figure 10. NCP3170 Enabled Current vs. Temperature

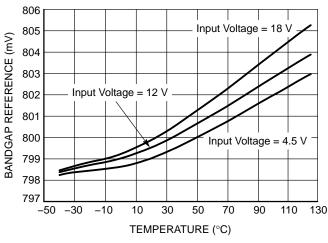

Figure 11. Bandgap Reference Voltage vs. Temperature

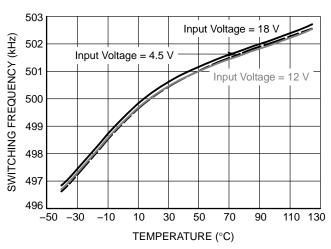

Figure 12. Switching Frequency vs.

Temperature

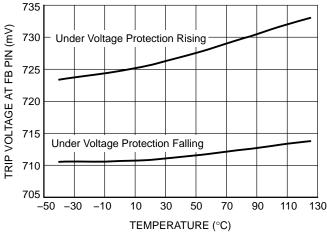

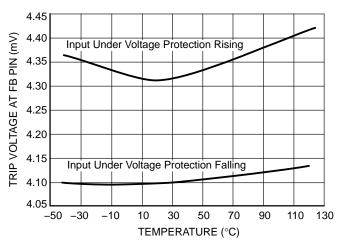

Figure 13. Input Under Voltage Protection at 12 V vs. Temperature

Figure 14. Input Over Voltage Protection at 12 V vs. Temperature

### TYPICAL PERFORMANCE CHARACTERISTICS

(Circuit from Figure 1,  $T_A = 25$ °C,  $V_{IN} = V_{EN} = 12$  V,  $V_{OUT} = 3.3$  V unless otherwise specified)

40 LOW SIDE MOSFET  $R_{DS(on)}$  (m $\Omega$ ) 35 30 Input Voltage = 4.5 V 25 Input Voltage = 12 V, 18 V 20 15 30 50 70 90 110 130 -30-1010 TEMPERATURE (°C)

Figure 15. High Side MOSFET  $R_{DS(on)}$  vs. Temperature

Figure 16. Low Side MOSFET  $R_{DS(on)}$  vs. Temperature

Figure 17. Transconductance vs. Temperature

Figure 18. Over Voltage Protection vs. Temperature

Figure 19. Input Under Voltage Protection vs. Temperature

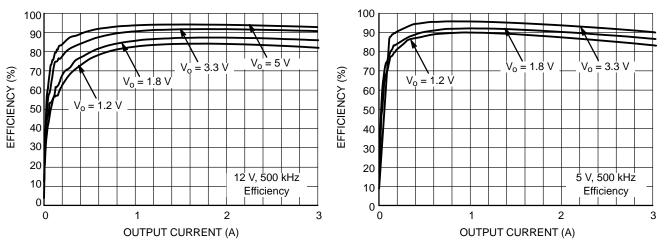

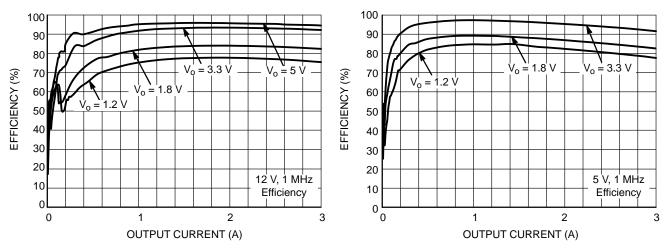

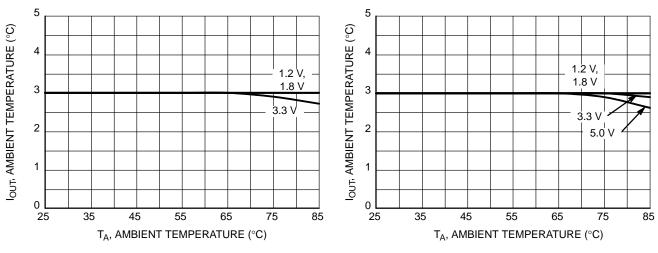

# NCP3170A Efficiency and Thermal Derating

Figure 20. Efficiency (V<sub>IN</sub> = 12 V) vs. Load Current

Figure 21. Efficiency (V<sub>IN</sub> = 5 V) vs. Load Current

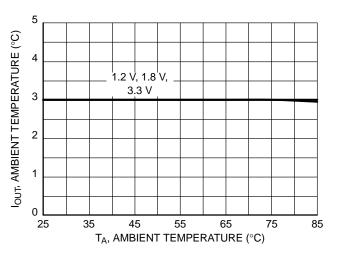

Thermal derating curves for the SOIC-8 package part under typical input and output conditions based on the evaluation board. The ambient temperature is  $25^{\circ}$ C with natural convection (air speed < 50 LFM) unless otherwise specified.

Figure 22. 500 kHz Derating Curves at 5 V

Figure 23. 500 kHz Derating Curves at 12 V

# NCP3170B Efficiency and Thermal Derating

Figure 24. 12 V, 1 MHz Efficiency

Figure 25. 5 V, 1 MHz Efficiency

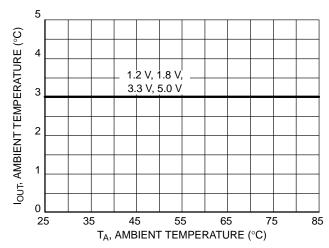

Thermal derating curves for the SOIC–8 package part under typical input and output conditions based on the evaluation board. The ambient temperature is 25°C with natural convection (air speed < 50 LFM) unless otherwise specified.

Figure 26. 1 MHz Derating Curves at 5 V Input

Figure 27. 1 MHz Derating Curves at 12 V Input

#### **DETAILED DESCRIPTION**

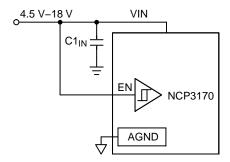

The NCP3170 is a current-mode, step down regulator with an integrated high-side PMOS switch and a low-side NMOS switch. It operates from a 4.5 V to 18 V input voltage range and supplies up to 3 A of load current. The duty ratio can be adjusted from 8% to 92% allowing a wide output voltage range. Features include enable control, Power-On Reset (POR), input under voltage lockout, fixed internal soft start, power good indication, over voltage protection, and thermal shutdown.

#### **Enable and Soft-Start**

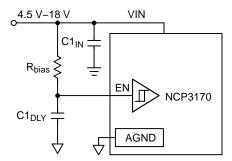

An internal input voltage comparator not shown in Figure 28 will force the part to disable below the minimum input voltage of 4.13 V. The input under voltage disable feature is used to prevent improper operation of the converter due to insufficient voltages. The converter can be turned on by tying the enable pin high and the part will default to be input voltage enabled. The enable pin should never be left floating.

Figure 28. Input Voltage Enable

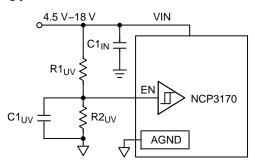

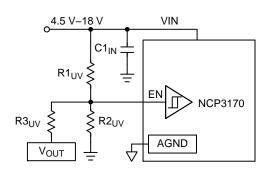

If an adjustable Under Voltage Lockout (UVLO) threshold is required, the EN pin can be used. The trip voltage of the EN pin comparator is 1.38 V typical. Upon application of an input voltage greater than 4.41 V, the VIN UVLO will release and the enable will be checked to determine if switching can commence. Once the 1.38 V trip voltage is crossed, the part will enable and the soft start sequence will initiate. If large resistor values are used, the EN pin should be bypassed with a 1 nF capacitor to prevent coupling problems from the switch node.

Figure 29. Input Under Voltage Lockout Enable

The enable pin can be used to delay a turn on by connecting a capacitor as shown in Figure 30.

Figure 30. Delay Enable

If the designer would like to add hysteresis to the enable threshold it can be added by use of a bias resistor to the output. The hysteresis is created once soft start has initiated. With the output voltage rising, current flows into the enable node, raising the voltage. The thresholds for enable as well as hysteresis can be calculated using Equation 1.

$$VIN_{HYS} = VIN_{Start} - EN_{TH} + R1_{UV} \times \left[ \frac{V_{OUT} - EN_{TH}}{R3_{UV}} - \frac{EN_{TH}}{R2_{UV}} \right]$$

(eq. 1)

$$VIN_{Start} = EN_{TH} \times \left[ 1 + \frac{R1_{UV} \times (R2_{UV} + R3_{UV})}{R2_{UV} \times R3_{UV}} \right] \quad (eq. 2)$$

where:

$EN_{TH}$  = Enable Threshold

VIN<sub>START</sub> = Input Voltage Start Threshold

$\begin{array}{ll} R1_{UV} & = High \ Side \ Resistor \\ R2_{UV} & = Low \ Side \ Resistor \\ R3_{UV} & = Hysteresis \ Bias \ Resistor \\ V_{OUT} & = Regulated \ Output \ Voltage \end{array}$

Figure 31. Added Hysteresis to the Enable UVLO

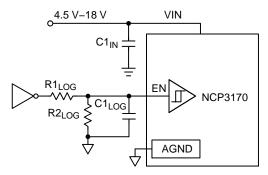

The part can be enabled with standard TTL or high voltage logic by using the configuration below.

Figure 32. Logic Turn-on

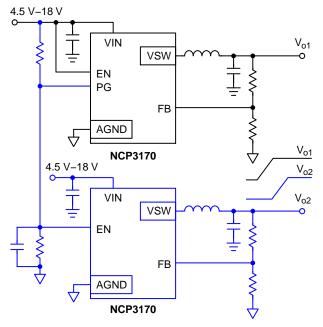

The enable can also be used for power sequencing in conjunction with the Power Good (PG) pin as shown in Figure 33. The enable pin can either be tied to the output voltage of the master voltage or tied to the input voltage with a resistor to the PG pin of the master regulator.

Figure 33. Enable Two Converter Power Sequencing

Once the part is enabled, the internal reference voltage is slewed from ground to the set point of 800 mV. The slewing process occurs over a 4.5 ms period, reducing the current draw from the upstream power source, reducing stress on internal MOSFETS, and ensuring the output inductor does not saturate during start-up.

### Pre-Bias Start-up

When starting into a pre-bias load, the NCP3170 will not discharge the output capacitors. The soft start begins with the internal reference at ground. Both the high side switch and low side switches are turned off. The internal reference

slowly raises and the OTA regulates the output voltage to the divided reference voltage. In a pre-biased condition, the voltage at the FB pin is higher than the internal reference voltage, so the OTA will keep the COMP voltage at ground potential. As the internal reference is slewed up, the COMP pin is held low until the FB pin voltage surpasses the internal reference voltage, at which time the COMP pin is allowed to respond to the OTA error signal. Since the bottom of the PWM ramp is at 0.6 V there will be a slight delay between the time the internal reference voltage passes the FB voltage and when the part starts to switch. Once the COMP error signal intersects with the bottom of the ramp, the high side switch is turned on followed by the low side switch. After the internal reference voltage has surpassed the FB voltage, soft start proceeds normally without output voltage discharge.

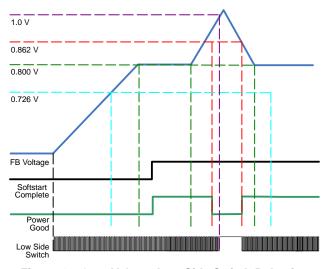

#### **Power Good**

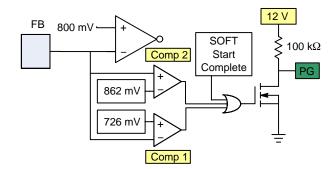

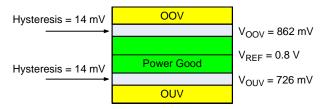

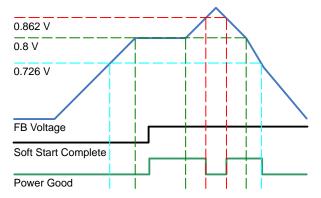

The output voltage of the buck converter is monitored at the feedback pin of the output power stage. Two comparators are placed on the feedback node of the OTA to monitor the operating window of the feedback voltage as shown in Figure 34. All comparator outputs are ignored during the soft start sequence as soft start is regulated by the OTA since false trips would be generated. Further, the PG pin is held low until the comparators are evaluated. PG state does not affect the switching of the converter. After the soft start period has ended, if the feedback is below the reference voltage of comparator 1 ( $V_{FB} < 0.726$ ), the output is considered operational undervoltage (OUV). The device will indicate the under voltage situation by the PG pin remaining low with a 100 k $\Omega$  pull-up resistance. When the feedback pin voltage rises between the reference voltages of comparator 1 and comparator 2  $(0.726 < V_{FB} < 0.862)$ , then the output voltage is considered power good and the PG pin is released. Finally, if the feedback voltage is greater than comparator 2  $(V_{FB} > 0.862)$ , the output voltage is considered operational overvoltage (OOV). The OOV will be indicated by the PG pin remaining low. A block diagram of the OOV and OUV functionality as well as a graphical representation of the PG pin functionality is shown in Figures 34 through 36.

Figure 34. OOV and OUV System

Figure 35. OOV and OUV Window

Figure 36. OOV and OUV Diagram

If the power good function is not used, it can be connected to the VSW node to reduce thermal resistance. Do not connect PG to the VSW node if the application is turning on into pre-bias.

### **Switching Frequency**

The NCP3170 switching frequency is fixed and set by an internal oscillator. The practical switching frequency could range from 450 kHz to 550 kHz for the NCP3170A and 900 kHz to 1.1 MHz for the NCP3170B due to device variation.

#### **Light Load Operation**

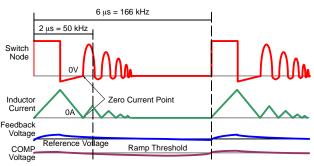

Light load operation is generally a load that is 1 mA to 300 mA where a load is in standby mode and requires very little power. During light load operation, the regulator emulates the operation of a non-synchronous buck converter and the regulator is allowed to skip pulses. The non-synchronous buck emulation is accomplished by detecting the point at which the current flowing in the inductor goes to zero and turning the low side switch off. At the point when the current goes to zero, if the low side switch is not turned off, current would reverse, discharging the output capacitor. Since the low side switch is shutoff, the only conduction path is through the body diode of the low side MOSFET, which is back biased. Unlike traditional synchronous buck converters, the current in the inductor will become discontinuous. As a result, the switch node will oscillate with the parasitic inductances and capacitances connected to the switch node. The OTA will continue to regulate the output voltage, but will skip pulses based on the output load shown in Figure 37.

Figure 37. Light Load Operation

#### **PROTECTION FEATURES**

# **Over Current Protection**

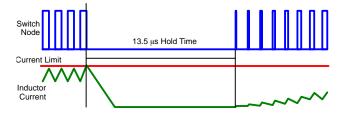

Current is limited to the load on a pulse by pulse basis. During each high side on period, the current is compared against an internally set limit. If the current limit is exceeded, the high side and low side MOSFETS are shutoff and no pulses are issued for 13.5 µs. During that time, the output voltage will decay and the inductor current will discharge. After the discharge period, the converter will initiate a soft start. If the load is not released, the current will build in the inductor until the current limit is exceeded, at which time the high side and low side MOSFETS will be shut off and the process will continue. If the load has been released, a normal soft start will commence and the part will continue switching normally until the current limit is exceeded.

**Figure 38. Over Current Protection**

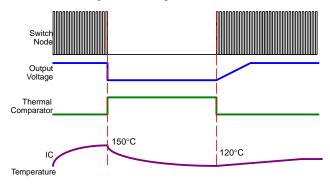

#### **Thermal Shutdown**

The thermal limit, while not a protection feature, engages at 150°C in case of thermal runaway. When the thermal comparator is tripped at a die temperature of 150°C, the part must cool to 120°C before a restart is allowed. When thermal

trip is engaged, switching ceases and high side and low side MOSFETs are driven off. Further, the power good indicator will pull low until the thermal trip has been released. Once the die temperature reaches 120°C the part will reinitiate soft-start and begin normal operation.

Figure 39. Over Temperature Shutdown

#### **Over Voltage Protection**

Upon the completion of soft start, the output voltage of the buck converter is monitored at the FB pin of the output power stage. One comparator is placed on the feedback node to provide over voltage protection. In the event an over voltage is detected, the high side switch turns off and the low side switch turns on until the feedback voltage falls below the OOV threshold. Once the voltage has fallen below the OOV threshold, switching continues normally as displayed in Figure 40.

Figure 40. Over Voltage Low Side Switch Behavior

# **Duty Ratio**

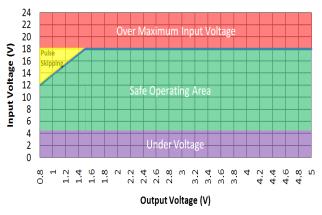

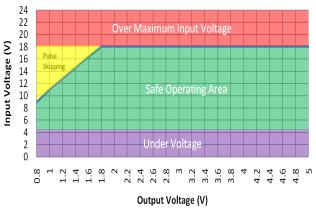

The duty ratio can be adjusted from 8% to 92% allowing a wide output voltage range. The low 8% duty ratio limit will restrict the PWM operation. For example if the application is converting to 1.2 V the converter will perform normally if the input voltage is below 15.5 V. If the input voltage exceeds 15.5 V while supplying 1.2 V output voltage the converter can skip pulses during operation. The skipping pulse operation will result in higher ripple voltage than when

operating in PWM mode. Figure 41 and 42 below shows the safe operating area for the NCP3170A and B respectively. While not shown in the safe operating area graph, the output voltage is capable of increasing to the 93% duty ratio limitation providing a high output voltage such as 16 V. If the application requires a high duty ratio such as converting from 14 V to 10 V the converter will operate normally until the maximum duty ratio is reached. For example, if the input voltage were 16 V and the user wanted to produce the highest possible output voltage at full load, a good rule of thumb is to use 80% duty ratio. The discrepancy between the usable duty ratio and the actual duty ratio is due to the voltage drops in the system, thus leading to a maximum output voltage of 12.8 V rather than 14.8 V. The actual achievable output to input voltage ratio is dependent on layout, component selection, and acceptable output voltage tolerance.

Figure 41. NCP3170A Safe Operating Area

Figure 42. NCP3170B Safe Operating Area

# **Design Procedure**

When starting the design of a buck regulator, it is important to collect as much information as possible about the behavior of the input and output before starting the design.

ON Semiconductor has a Microsoft Excel<sup>®</sup> based design tool available online under the design tools section of the NCP3170 product page. The tool allows you to capture your

design point and optimize the performance of your regulator based on your design criteria.

**Table 5. DESIGN PARAMETERS**

| Design Parameter                                | Example Value |

|-------------------------------------------------|---------------|

| Input Voltage (V <sub>IN</sub> )                | 9 V to 16 V   |

| Output Voltage (V <sub>OUT</sub> )              | 3.3 V         |

| Input Ripple Voltage (VCC <sub>RIPPLE</sub> )   | 200 mV        |

| Output Ripple Voltage (V <sub>OUTRIPPLE</sub> ) | 20 mV         |

| Output Current Rating (I <sub>OUT</sub> )       | 3 A           |

| Operating Frequency (F <sub>SW</sub> )          | 500 kHz       |

The buck converter produces input voltage ( $V_{IN}$ ) pulses that are LC filtered to produce a lower DC output voltage ( $V_{OUT}$ ). The output voltage can be changed by modifying the on time relative to the switching period (T) or switching frequency. The ratio of high side switch on time to the switching period is called duty ratio (D). Duty ratio can also be calculated using  $V_{OUT}$ ,  $V_{IN}$ , the Low Side Switch Voltage Drop ( $V_{LSD}$ ), and the High Side Switch Voltage Drop ( $V_{HSD}$ ).

$$F_{SW} = \frac{1}{T}$$

(eq. 3)

$$D = \frac{T_{ON}}{T}(1 - D) = \frac{T_{OFF}}{T}$$

(eq. 4)

$$D = \frac{V_{OUT} + V_{LSD}}{V_{IN} - V_{HSD} + V_{LSD}} \approx D = \frac{V_{OUT}}{V_{IN}} \Rightarrow 27.5\% = \frac{3.3 \text{ V}}{12 \text{ V}}$$

(eq. 5)

where:

D = Duty ratio

FSW = Switching frequency

T = Switching period

TOFF = High side switch off time

TON = High side switch on time

$V_{IN}$  = Input voltage

VHSD = High side switch voltage drop VLSD = Low side switch voltage drop

VOUT = Output voltage

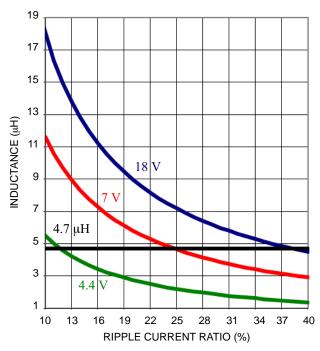

### **Inductor Selection**

When selecting an inductor, the designer may employ a rule of thumb for the design where the percentage of ripple current in the inductor should be between 10% and 40%. When using ceramic output capacitors, the ripple current can be greater because the ESR of the output capacitor is smaller, thus a user might select a higher ripple current. However, when using electrolytic capacitors, a lower ripple current will result in lower output ripple due to the higher ESR of electrolytic capacitors. The ratio of ripple current to maximum output current is given in Equation 6.

$$ra = \frac{\Delta I}{I_{OUT}}$$

(eq. 6)

where:

$\Delta I$  = Ripple current  $I_{OUT}$  = Output current ra = Ripple current ratio

Using the ripple current rule of thumb, the user can establish acceptable values of inductance for a design using Equation 6.

$$L_{OUT} = \frac{V_{OUT}}{I_{OUT} \times ra \times F_{SW}} \times (1 - D) \rightarrow$$

$$4.7\mu H = \frac{12 \text{ V}}{3.0 \text{ A} \times 34\% \times 500 \text{ kHz}} \times (1 - 27.5\%)$$

(eq. 7)

where:

D = Duty ratio

$\begin{array}{ll} F_{SW} & = Switching \ frequency \\ I_{OUT} & = Output \ current \\ L_{OUT} & = Output \ inductance \\ ra & = Ripple \ current \ ratio \end{array}$

Figure 43. Inductance vs. Current Ripple Ratio

When selecting an inductor, the designer must not exceed the current rating of the part. To keep within the bounds of the part's maximum rating, a calculation of the RMS current and peak current are required.

$$I_{RMS} = I_{OUT} \times \sqrt{1 + \frac{ra^2}{12}} \rightarrow$$

(eq. 8)

$3.01 A = 3 A \times \sqrt{1 + \frac{34\%^2}{12}} \rightarrow$

where:

$\begin{array}{ll} I_{OUT} & = Output \ current \\ I_{RMS} & = Inductor \ RMS \ current \\ ra & = Ripple \ current \ ratio \\ \end{array}$

$$I_{PK} = I_{OUT} \times \left(1 + \frac{ra}{2}\right) \rightarrow$$

$$3.51 A = 3 A \times \left(1 + \frac{34\%}{2}\right)$$

(eq. 9)

where:

$\begin{array}{ll} I_{OUT} & = Output \ current \\ I_{PK} & = Inductor \ peak \ current \\ ra & = Ripple \ current \ ratio \end{array}$

A standard inductor should be found so the inductor will be rounded to 4.7  $\mu$ H. The inductor should support an RMS current of 3.01 A and a peak current of 3.51 A. A good design practice is to select an inductor that has a saturation current that exceeds the maximum current limit with some margin.

The final selection of an output inductor has both mechanical and electrical considerations. From a mechanical perspective, smaller inductor values generally correspond to smaller physical size. Since the inductor is often one of the largest components in the regulation system, a minimum inductor value is particularly important in space constrained applications. From an electrical perspective, the maximum current slew rate through the output inductor for a buck regulator is given by Equation 10.

$$SlewRate_{LOUT} = \frac{V_{IN} - V_{OUT}}{L_{OUT}} \rightarrow$$

$$1.85 \frac{A}{\mu s} = \frac{12 \ V - 3.3 \ V}{4.7 \mu H}$$

(eq. 10)

where:

$\begin{array}{ll} L_{OUT} & = \text{Output inductance} \\ V_{IN} & = \text{Input voltage} \\ V_{OUT} & = \text{Output voltage} \\ \end{array}$

Equation 10 implies that larger inductor values limit the regulator's ability to slew current through the output inductor in response to output load transients. Consequently, output capacitors must supply the load current until the inductor current reaches the output load current level. Reduced inductance to increase slew rates results in larger values of output capacitance to maintain tight output voltage regulation. In contrast, smaller values of inductance increase the regulator's maximum achievable slew rate and decrease the necessary capacitance at the expense of higher ripple current. The peak-to-peak ripple current for NCP3170 is given by the following equation:

$$I_{PP} = \frac{V_{OUT} \times (1 - D)}{L_{OUT} \times F_{SW}} \rightarrow$$

$$1.02 A = \frac{3.3 \text{ V} \times (1 - 27.5\%)}{4.7 \text{ uH} \times 500 \text{ kHz}}$$

(eq. 11)

where:

D = Duty ratio

F<sub>SW</sub> = Switching frequency

I<sub>PP</sub> = Peak-to-peak current of the inductor

$\begin{array}{ll} L_{OUT} & = Output \ inductance \\ V_{OUT} & = Output \ voltage \end{array}$

From Equation 11, it is clear that the ripple current increases as L<sub>OUT</sub> decreases, emphasizing the trade-off between dynamic response and ripple current.

The power dissipation of an inductor falls into two categories: copper and core losses. Copper losses can be further categorized into DC losses and AC losses. A good first order approximation of the inductor losses can be made using the DC resistance as shown below:

$$LP_{CU\_DC} = I_{RMS}^{2} \times DCR \rightarrow$$

(eq. 12)

61 mW = 3.01<sup>2</sup> × 6.73 mΩ

where:

DCR = Inductor DC resistance I<sub>RMS</sub> = Inductor RMS current

LP<sub>CU\_DC</sub> = Inductor DC power dissipation

The core losses and AC copper losses will depend on the geometry of the selected core, core material, and wire used. Most vendors will provide the appropriate information to make accurate calculations of the power dissipation at which point the total inductor losses can be captured by the equation below:

$$LP_{tot} = LP_{CU\_DC} + LP_{CU\_AC} + LP_{Core} \rightarrow$$

$$67 mW = 61 mW + 5 mW + 1 mW$$

(eq. 13)

where:

$\begin{array}{ll} LP_{Core} & = Inductor \ core \ power \ dissipation \\ LP_{CU\_AC} & = Inductor \ AC \ power \ dissipation \\ LP_{CU\_DC} & = Inductor \ DC \ power \ dissipation \end{array}$

$LP_{tot}$  = Total inductor losses

### **Output Capacitor Selection**

The important factors to consider when selecting an output capacitor are DC voltage rating, ripple current rating, output ripple voltage requirements, and transient response requirements.

The output capacitor must be able to operate properly for the life time of a product. When selecting a capacitor it is important to select a voltage rating that is de-rated to the guaranteed operating life time of a product. Further, it is important to note that when using ceramic capacitors, the capacitance decreases as the voltage applied increases; thus a ceramic capacitor rated at  $100~\mu F 6.3~V$  may measure

$100 \mu F$  at 0 V but measure  $20 \mu F$  with an applied voltage of 3.3 V depending on the type of capacitor selected.

The output capacitor must be rated to handle the ripple current at full load with proper derating. The capacitor RMS ratings given in datasheets are generally for lower switching frequencies than used in switch mode power supplies, but a multiplier is given for higher frequency operation. The RMS current for the output capacitor can be calculated below:

$$CO_{RMS} = I_{OUT} \frac{ra}{\sqrt{12}} \rightarrow$$

$$0.294 A = 3.0 A \frac{34\%}{\sqrt{12}}$$

(eq. 14)

where:

Co<sub>RMS</sub> = Output capacitor RMS current

I<sub>OUT</sub> = Output current ra = Ripple current ratio

The maximum allowable output voltage ripple is a combination of the ripple current selected, the output capacitance selected, the Equivalent Series Inductance (ESL), and Equivalent Series Resistance (ESR).

The main component of the ripple voltage is usually due to the ESR of the output capacitor and the capacitance selected, which can be calculated as shown in Equation 14:

$$V_{ESR\_C} = I_{OUT} \times ra \times \left( CO_{ESR} + \frac{1}{8 \times F_{SW} \times C_{OUT}} \right) \rightarrow$$

(eg. 15)

10.89 mV =

$$3 \times 34\% \times \left(5 \text{ m}\Omega + \frac{1}{8 \times 500 \text{ kHz} \times 44 \mu\text{F}}\right)^{-1}$$

where:

$\begin{array}{lll} Co_{ESR} & = Output \ capacitor \ ESR \\ C_{OUT} & = Output \ capacitance \\ F_{SW} & = Switching \ frequency \\ I_{OUT} & = Output \ current \\ ra & = Ripple \ current \ ratio \end{array}$

$V_{ESR\ C}$  = Ripple voltage from the capacitor

The impedance of a capacitor is a function of the frequency of operation. When using ceramic capacitors, the ESR of the capacitor decreases until the resonant frequency is reached, at which point the ESR increases; therefore the ripple voltage might not be what one expected due to the switching frequency. Further, the method of layout can add resistance in series with the capacitance, increasing ripple voltage.

The ESL of capacitors depends on the technology chosen, but tends to range from 1 nH to 20 nH, where ceramic capacitors have the lowest inductance and electrolytic capacitors have the highest. The calculated contributing voltage ripple from ESL is shown for the switch on and switch off below:

$$V_{ESLON} = \frac{ESL \times I_{PP} \times F_{SW}}{D} \rightarrow$$

$$1.84 \text{ mV} = \frac{1 \text{ nH} \cdot 1.01 \text{ A} \cdot 500 \text{ kHz}}{27.5\%}$$

(eq. 16)

$$V_{ESLOFF} = \frac{ESL \times I_{PP} \times F_{SW}}{(1 - D)} \rightarrow$$

$$0.7 \text{ mV} = \frac{1 \text{ nH} \times 1.1 \text{ A} \times 500 \text{ kHz}}{(1 - 27.5\%)}$$

(eq. 17)

where:

D = Duty ratio

$\begin{array}{ll} ESL & = Capacitor \ inductance \\ F_{SW} & = Switching \ frequency \\ I_{PP} & = Peak-to-peak \ current \end{array}$

The output capacitor is a basic component for fast response of the power supply. For the first few microseconds of a load transient, the output capacitor supplies current to the load. Once the regulator recognizes a load transient, it adjusts the duty ratio, but the current slope is limited by the inductor value.

During a load step transient, the output voltage initially drops due to the current variation inside the capacitor and the ESR (neglecting the effect of the ESL).

$$\Delta V_{OUT-ESR} = I_{TRAN} \times CO_{ESR} \rightarrow$$

$$7.5 \text{ mV} = 1.5 \text{ A} \times 5 \text{ m}\Omega$$

(eq. 18)

where:

Co<sub>ESR</sub> = Output capacitor Equivalent Series

Resistance

I<sub>TRAN</sub> = Output transient current

$\Delta V_{OUT\_ESR}$  = Voltage deviation of  $V_{OUT}$  due to the

effects of ESR

A minimum capacitor value is required to sustain the current during the load transient without discharging it. The voltage drop due to output capacitor discharge is given by the following equation:

$$\Delta V_{OUT-DIS} = \frac{\left(I_{TRAN}\right)^{2} \times L_{OUT} \times F_{SW}}{2 \times F_{CROSS} \times C_{OUT} \times \left(V_{IN} - V_{OUT}\right)} \rightarrow (eq. 19)$$

$$138.1 \text{ mV} = \frac{\left(1.5\right)^{2} \times 4.7 \,\mu\text{H} \times 500 \text{ kHz}}{2 \times 50 \text{ kHz} \times 44 \,\mu\text{F} \times \left(12 \text{ V} - 3.3 \text{ V}\right)}$$

where:

C<sub>OUT</sub> = Output capacitance

D = Duty ratio

$\begin{array}{ll} F_{SW} & = Switching \ frequency \\ F_{CROSS} & = Loop \ cross \ over \ frequency \\ I_{TRAN} & = Output \ transient \ current \\ L_{OUT} & = Output \ inductor \ value \end{array}$

$V_{IN}$  = Input voltage  $V_{OUT}$  = Output voltage

$\Delta V_{OUT\_DIS}$  = Voltage deviation of  $V_{OUT}$  due to the

effects of capacitor discharge

In a typical converter design, the ESR of the output capacitor bank dominates the transient response. Please note that  $\Delta V_{OUT\_DIS}$  and  $\Delta V_{OUT\_ESR}$  are out of phase with each other, and the larger of these two voltages will determine the maximum deviation of the output voltage (neglecting the effect of the ESL). It is important to note that the converters frequency response will change when the NCP3170 is operating in synchronous mode or non-synchronous mode due to the change in plant response from CCM to DCM. The effect will be a larger transient voltage excursion when transitioning from no load to full load quickly.

#### **Input Capacitor Selection**

The input capacitor has to sustain the ripple current produced during the on time of the upper MOSFET, so it must have a low ESR to minimize losses and input voltage ripple. The RMS value of the input ripple current is:

$$lin_{RMS} = I_{OUT} \times \sqrt{D \times (1 - D)} \rightarrow$$

(eq. 20)

1.34  $A = 3 A \times \sqrt{27.5\% \times (1 - 27.5\%)}$

where:

D = Duty ratio

Iin<sub>RMS</sub> = Input capacitance RMS current

$I_{OUT}$  = Load current

The equation reaches its maximum value with D=0.5 at which point the input capacitance RMS current is half the output current. Loss in the input capacitors can be calculated with the following equation:

$$P_{CIN} = CIN_{ESR} \times \left(Iin_{RMS}\right)^{2}$$

$$18 \text{ mW} = 10 \text{ m}\Omega \times \left(1.34 \text{ A}\right)^{2}$$

(eq. 21)

where:

CIN<sub>ESR</sub> = Input capacitance Equivalent Series

Resistance

$Iin_{RMS}$  = Input capacitance RMS current  $P_{CIN}$  = Power loss in the input capacitor

Due to large di/dt through the input capacitors, electrolytic or ceramics should be used. If a tantalum capacitor must be used, it must be surge protected, otherwise capacitor failure could occur.

#### POWER MOSFET DISSIPATION

Power dissipation, package size, and the thermal environment drive power supply design. Once the dissipation is known, the thermal impedance can be calculated to prevent the specified maximum junction temperatures from being exceeded at the highest ambient temperature.

Power dissipation has two primary contributors: conduction losses and switching losses. The high-side MOSFET will display both switching and conduction losses. The switching losses of the low side MOSFET will not be calculated as it switches into nearly zero voltage and the losses are insignificant. However, the body diode in the low-side MOSFET will suffer diode losses during the non-overlap time of the gate drivers.

Starting with the high-side MOSFET, the power dissipation can be approximated from:

$$P_{D HS} = P_{COND} + P_{SW TOT}$$

(eq. 22)

where:

$P_{COND}$  = Conduction losses

$P_{D-HS}$  = Power losses in the high side MOSFET

$P_{SW-TOT}$  = Total switching losses

The first term in Equation 21 is the conduction loss of the high-side MOSFET while it is on.

$$P_{COND} = \left(I_{RMS, HS}\right)^2 \times R_{DS(op), HS}$$

(eq. 23)

where:

$I_{RMS\_HS}$  = RMS current in the high side MOSFET  $R_{DS(ON)\_HS}$  = On resistance of the high side MOSFET

$P_{COND}$  = Conduction power losses

Using the ra term from Equation 6, I<sub>RMS</sub> becomes:

$$I_{RMS\_HS} = I_{OUT} \times \sqrt{D \times \left(1 + \frac{ra^2}{12}\right)}$$

(eq. 24)

where:

D = Duty ratio

$\begin{array}{ll} \text{ra} & = \text{Ripple current ratio} \\ \text{I}_{OUT} & = \text{Output current} \\ \end{array}$

I<sub>RMS\_HS</sub> = High side MOSFET RMS current

The second term from Equation 22 is the total switching loss and can be approximated from the following equations.

$$P_{SW\ TOT} = P_{SW} + P_{DS} + P_{RR} \qquad (eq.\ 25)$$

where:

$P_{DS}$  = High side MOSFET drain to source losses

P<sub>RR</sub> = High side MOSFET reverse recovery

losses

P<sub>SW</sub> = High side MOSFET switching losses

P<sub>SW TOT</sub> = High side MOSFET total switching losses

The first term for total switching losses from Equation 25 are the losses associated with turning the high-side MOSFET on and off and the corresponding overlap in drain voltage and current.

$$\begin{split} P_{SW} &= P_{TON} + P_{TOFF} = \\ &= \frac{1}{2} \times \left( I_{OUT} \times V_{IN} \times F_{SW} \right) \times \left( t_{RISE} + t_{FALL} \right) \end{split} \tag{eq. 26}$$

where:

$F_{SW}$  = Switching frequency

$I_{OUT}$  = Load current

P<sub>SW</sub> = High side MOSFET switching losses

$\begin{array}{ll} P_{TON} & = Turn \ on \ power \ losses \\ P_{TOFF} & = Turn \ off \ power \ losses \\ t_{FALL} & = MOSFET \ fall \ time \\ t_{RISE} & = MOSFET \ rise \ time \\ V_{IN} & = Input \ voltage \end{array}$

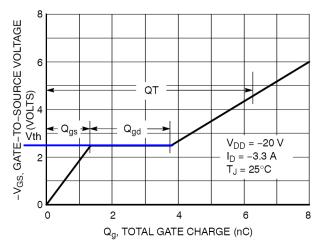

When calculating the rise time and fall time of the high side MOSFET, it is important to know the charge characteristic shown in Figure 44.

Figure 44. High Side MOSFET Total Charge

$$t_{RISE} = \frac{Q_{GD}}{I_{G1}} = \frac{Q_{GD}}{(V_{CI} - V_{TH})/(R_{HSPIJ} + R_G)}$$

(eq. 27)

where:

IG1 = Output current from the high-side gate

drive

Q<sub>GD</sub> = MOSFET gate to drain gate charge

$\begin{array}{ll} R_{HSPU} & = Drive \ pull \ up \ resistance \\ R_G & = MOSFET \ gate \ resistance \\ t_{RISE} & = MOSFET \ rise \ time \\ V_{CL} & = Clamp \ voltage \end{array}$

V<sub>TH</sub> = MOSFET gate threshold voltage

$$t_{FALL} = \frac{Q_{GD}}{I_{G2}} = \frac{Q_{GD}}{(V_{CL} - V_{TH})/(R_{HSPD} + R_G)} \qquad (eq.~28)$$

where:

IG2 = Output current from the low-side gate

drive

$Q_{GD}$  = MOSFET gate to drain gate charge

R<sub>G</sub> = MOSFET gate resistance R<sub>HSPD</sub> = Drive pull down resistance

$t_{FALL}$  = MOSFET fall time  $V_{CL}$  = Clamp voltage

V<sub>TH</sub> = MOSFET gate threshold voltage

Next, the MOSFET output capacitance losses are caused by both the high-side and low-side MOSFETs, but are dissipated only in the high-side MOSFET.

$$P_{DS} = \frac{1}{2} \times C_{OSS} \times V_{IN}^2 \times F_{SW}$$

(eq. 29)

where:

$C_{OSS}$  = MOSFET output capacitance at 0 V

$F_{SW}$  = Switching frequency

P<sub>DS</sub> = MOSFET drain to source charge losses

$V_{IN}$  = Input voltage

Finally, the loss due to the reverse recovery time of the body diode in the low-side MOSFET is shown as follows:

$$P_{RR} = Q_{RR} \times V_{IN} \times F_{SW} \qquad (eq. 30)$$

where:

$F_{SW}$  = Switching frequency

P<sub>RR</sub> = High side MOSFET reverse recovery

losses

$Q_{RR}$  = Reverse recovery charge

$V_{IN}$  = Input voltage

The low-side MOSFET turns on into small negative voltages so switching losses are negligible. The low-side MOSFET's power dissipation only consists of conduction loss due to  $R_{\mathrm{DS(on)}}$  and body diode loss during non-overlap periods.

$$P_{D,LS} = P_{COND} + P_{BODY}$$

(eq. 31)

where:

$P_{BODY}$  = Low side MOSFET body diode losses  $P_{COND}$  = Low side MOSFET conduction losses

$P_{D LS}$  = Low side MOSFET losses

Conduction loss in the low-side MOSFET is described as follows:

$$P_{COND} = \left(I_{RMS\_LS}\right)^2 \times R_{DS(on)\_LS}$$

(eq. 32)

where:

$\begin{array}{ll} I_{RMS\_LS} & = RMS \ current \ in \ the \ low \ side \\ R_{DS(ON)\_LS} & = Low\mbox{-side MOSFET on resistance} \\ P_{COND} & = High \ side \ MOSFET \ conduction \ losses \\ \end{array}$

$$I_{RMS\_LS} = I_{OUT} \times \sqrt{(1-D) \times \left(1 + \frac{ra^2}{12}\right)}$$

(eq. 33)

where:

$\begin{array}{ll} D & = Duty \ ratio \\ I_{OUT} & = Load \ current \end{array}$

$I_{RMS LS}$  = RMS current in the low side

ra = Ripple current ratio

The body diode losses can be approximated as:

$P_{BODY} = V_{FD} \times I_{OUT} \times F_{SW} \times (NOL_{LH} + NOL_{HL})$  (eq. 34)

where:

F<sub>SW</sub> = Switching frequency

$I_{OUT}$  = Load current

NOL<sub>HI</sub> = Dead time between the high-side

MOSFET turning off and the low-side MOSFET turning on, typically 30 ns

NOLLH = Dead time between the low-side

MOSFET turning off and the high-side

MOSFET turning on, typically 30 ns

P<sub>BODY</sub> = Low-side MOSFET body diode losses

$V_{FD}$  = Body diode forward voltage drop

typically 0.92 V

#### **Compensation Network**

To create a stable power supply, the compensation network around the transconductance amplifier must be used in conjunction with the PWM generator and the power stage. Since the power stage design criteria is set by the application, the compensation network must correct the overall output to ensure stability. The NCP3170 is a current mode regulator and as such there exists a voltage loop and a current loop. The current loop causes the inductor to act like a current source which governs most of the characteristics of current mode control. The output inductor and capacitor of the power stage form a double pole but because the inductor is treated like a current source in closed loop, it becomes a single pole system. Since the feedback loop is controlling the inductor current, it is effectively like having a current source feeding a capacitor; therefore the pole is controlled by the load and the output capacitance. A table of compensation values for 500 kHz and 1 MHz is provided below for two 22 µF ceramic capacitors. The table also provides the resistor value for CompCalc at the defined operating point.

**Table 6. COMPENSATION VALUES**

|          | VIN<br>(V) | V <sub>out</sub><br>(V) | L <sub>out</sub><br>(μF) | R1<br>(kΩ) | R2<br>(kΩ) | Rf<br>(kΩ) | Cf<br>(pF) | Cc<br>(nF) | Rc<br>(kΩ) | Cp<br>(pF) | Resistance for<br>Current Gain |

|----------|------------|-------------------------|--------------------------|------------|------------|------------|------------|------------|------------|------------|--------------------------------|

|          | 12         | 0.8                     | 1.8                      | 24.9       | NI         | NI         | NI         | NI         | NI         | 15         | 3.6                            |

|          | 12         | 1.0                     | 2.5                      | 24.9       | 100        | 1          | 150        | 15         | 0.825      | NI         | 4                              |

|          | 12         | 1.1                     | 2.5                      | 24.9       | 66.5       | 1          | 150        | 10         | 2          | NI         | 20                             |

|          | 12         | 1.2                     | 2.5                      | 24.9       | 49.9       | 1          | 150        | 10         | 2          | NI         | 20                             |

|          | 12         | 1.5                     | 3.6                      | 24.9       | 28.7       | 1          | 150        | 10         | 2.49       | NI         | 20                             |

|          | 12         | 1.8                     | 3.6                      | 24.9       | 20         | 1          | 150        | 10         | 2.49       | NI         | 20                             |

|          | 12         | 2.5                     | 4.7                      | 24.9       | 11.8       | 1          | 150        | 8.2        | 3.74       | NI         | 25                             |

|          | 12         | 3.3                     | 4.7                      | 24.9       | 7.87       | 1          | 150        | 6.8        | 4.99       | NI         | 27                             |

|          | 12         | 5.0                     | 7.2                      | 24.9       | 4.75       | 1          | 150        | 3.9        | 10         | NI         | 27                             |

| NCP3170A | 12         | 10.68                   | 7.2                      | 24.9       | 2.05       | 1          | 150        | 3.9        | 10         | NI         | 30                             |

|          | 18         | 14.8                    | 7.2                      | 24.9       | 1.43       | 1          | 150        | 6.8        | 6.98       | NI         | 30                             |

|          | 5          | 0.8                     | 1.8                      | 24.9       | NI         | NI         | NI         | NI         | NI         | 15         | 15                             |

|          | 5          | 1.0                     | 2.5                      | 24.9       | 100        | 1          | 150        | 15         | 0.825      | NI         | 28                             |

|          | 5          | 1.1                     | 2.5                      | 24.9       | 66.5       | 1          | 150        | 10         | 2          | NI         | 30                             |

|          | 5          | 1.2                     | 2.5                      | 24.9       | 49.9       | 1          | 150        | 10         | 2          | NI         | 30                             |

|          | 5          | 1.5                     | 3.6                      | 24.9       | 28.7       | 1          | 150        | 10         | 2.49       | NI         | 30                             |

|          | 5          | 1.8                     | 3.6                      | 24.9       | 20         | 1          | 150        | 10         | 2.49       | NI         | 30                             |

|          | 5          | 2.5                     | 3.6                      | 24.9       | 11.8       | 1          | 150        | 6.8        | 4.99       | NI         | 50                             |

|          | 5          | 3.3                     | 3.6                      | 24.9       | 7.87       | 1          | 150        | 6.8        | 4.99       | NI         | 50                             |

Table 6. COMPENSATION VALUES (continued)

|          | VIN | V <sub>out</sub> | L <sub>out</sub> | R1   | R2            | Rf   | Cf   | Сс   | Rc            | Ср   | Resistance for |

|----------|-----|------------------|------------------|------|---------------|------|------|------|---------------|------|----------------|

|          | (V) | (V)              | (μ <b>F</b> )    | (kΩ) | (k $\Omega$ ) | (kΩ) | (pF) | (nF) | (k $\Omega$ ) | (pF) | Current Gain   |

|          | 12  | 1.2              | 1.5              | 24.9 | 49.9          | 1    | 82   | 2.7  | 6.04          | NI   | 20             |

|          | 12  | 1.5              | 1.8              | 24.9 | 28.7          | 1    | 82   | 2.7  | 6.04          | NI   | 22             |

|          | 12  | 1.8              | 1.8              | 24.9 | 20            | 1    | 82   | 2.7  | 6.04          | NI   | 22             |

|          | 12  | 2.5              | 2.7              | 24.9 | 11.8          | 1    | 82   | 1.8  | 10            | NI   | 32             |

|          | 12  | 3.3              | 3.3              | 24.9 | 7.87          | 1    | 82   | 1.5  | 12.1          | NI   | 52             |

|          | 12  | 5.0              | 3.3              | 24.9 | 4.75          | 1    | 82   | 2.2  | 8.25          | NI   | 52             |

|          | 12  | 10.68            | 1.5              | 24.9 | 2.05          | 1    | 82   | 2.2  | 5.1           | NI   | 52             |

| NCP3170B | 18  | 14.8             | 3.3              | 24.9 | 1.43          | 1    | 82   | 2.2  | 5.1           | NI   | 52             |

| NCP3170B | 5   | 0.8              | 1.0              | 24.9 | NI            | NI   | NI   | 15   | 0.499         | NI   | 20             |

|          | 5   | 1.0              | 1.0              | 24.9 | 100           | NI   | NI   | 6.8  | 1.69          | NI   | 28             |

|          | 5   | 1.1              | 1.0              | 24.9 | 66.5          | NI   | NI   | 3.9  | 3.61          | NI   | 42             |

|          | 5   | 1.2              | 1.5              | 24.9 | 49.9          | 1    | 82   | 2.7  | 6.04          | NI   | 55             |

|          | 5   | 1.5              | 1.5              | 24.9 | 28.7          | 1    | 82   | 2.7  | 6.04          | NI   | 55             |

|          | 5   | 1.8              | 1.5              | 24.9 | 20            | 1    | 82   | 1.8  | 10            | NI   | 55             |

|          | 5   | 2.5              | 1.8              | 24.9 | 11.8          | 1    | 82   | 1.8  | 10            | NI   | 55             |

|          | 5   | 3.3              | 1.8              | 24.9 | 7.87          | 1    | 82   | 1.8  | 10            | NI   | 55             |

To compensate the converter we must first calculate the current feedback

$$M = \frac{F_{SW} \times L_{OUT} \times V_{RAMP}}{R_{MAP} \times VIN} + 1 \to$$

(eq. 35)

$$6.299 = \frac{500 \text{ kHz} \times 4.7 \mu H \times 0.33 \text{ V}}{\left(32 \times \frac{3.3 \text{ V}}{12 \text{ V}} + 1.46\right)} + 1$$

where:

$\begin{array}{lll} F_{SW} & = Switching \ Frequency \\ L_{OUT} & = Output \ inductor \ value \\ M & = Current \ feedback \\ Vin & = Input \ Voltage \\ V_{OUT} & = Output \ Voltage \end{array}$

$V_{RAMP}$  = Slope Compensation Ramp  $R_{MAP}$  = Current Sense Resistance

The un-scaled gain of the converter also needs to be calculated as follows:

$$A = \frac{1}{\frac{I_{OUT}}{V_{OUT}} + \frac{M - 0.5 - M \times \frac{V_{OUT}}{V_{IN}}}{L_{OUT} \times FSW}}$$

$$0.379 \Omega = \frac{1}{\frac{3.0 \text{ A}}{3.3 \text{ V}} + \frac{6.299 - 0.5 - 6.299 \times \frac{3.3 \text{ V}}{12 \text{ V}}}{4.7 \mu \text{H} \times 500 \text{ kHz}}}$$

(eq. 36)

where:

$\begin{array}{lll} A & = \text{Un-scaled gain} \\ F_{SW} & = \text{Switching Frequency} \\ I_{OUT} & = \text{Output Current} \\ L_{OUT} & = \text{Output inductor value} \\ M & = \text{Current feedback} \\ V_{IN} & = \text{Input Voltage} \\ V_{OUT} & = \text{Output Voltage} \\ \end{array}$

Next the DC gain of the plant must be calculated.

$$G = \frac{A}{R_{MAP}} \rightarrow$$

$$36.925 = \frac{0.379 \,\Omega}{\left(32 \times \frac{3.3 \,V}{12 \,V} + 1.46\right)} \,\Omega$$

(eq. 37)

where:

G = DC gain of the plant A = Un-scaled gain

The amplitude ratio can be calculated using the following equation:

$$Y = \frac{VREF}{V_{OUT}} \rightarrow 0.242 = \frac{0.8 \text{ V}}{3.3 \text{ V}}$$

(eq. 38)

where:

Vo = Output voltage

VREF = Regulator reference voltage

Y = Amplitude ratio

The ESR of the output capacitor creates a "zero" at the frequency as shown in Equation 39:

$$FZ_{ESR} = \frac{1}{2\pi \times CO_{ESR} \times C_{OUT}} \rightarrow$$

$$723 \text{ kHz} = \frac{1}{2\pi \times 5 \text{ m}\Omega \times 44 \mu\text{F}}$$

(eq. 39)

where:

$CO_{ESR}$  = Output capacitor ESR  $C_{OUT}$  = Output capacitor

FZ<sub>ESR</sub> = Output capacitor zero ESR frequency

$$F_P = \frac{1}{2\pi \times A \times C_{OUT}} \Rightarrow$$

(eq. 40)

$$9.548 \text{ kHz} = \frac{1}{2\pi \times 0.379 \,\Omega \times 44 \,\mu\text{F}}$$

where:

$\begin{array}{ll} A & = \mbox{Un-scaled gain} \\ C_{OUT} & = \mbox{Output capacitor} \end{array}$

$F_P$  = Current mode pole frequency

The two equations above define the bode plot that the power stage has created or open loop response of the system. The next step is to close the loop by considering the feedback values. The closed loop crossover frequency should be less than 1/10 of the switching frequency, which would place the maximum crossover frequency at 50 kHz.

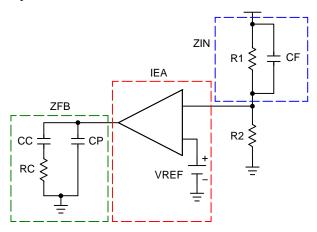

Figure 45 shows a pseudo Type III transconductance error amplifier.

Figure 45. Pseudo Type III Transconductance Error Amplifier

The compensation network consists of the internal error amplifier and the impedance networks  $Z_{IN}$  ( $R_1$ ,  $R_2$ , and  $C_F$ ) and external  $Z_{FB}$  ( $R_C$ ,  $C_C$ , and  $C_P$ ). The compensation network has to provide a closed loop transfer function with the highest 0 dB crossing frequency to have fast response and the highest gain in DC conditions, so as to minimize load regulation issues. A stable control loop has a gain crossing with -20 dB/decade slope and a phase margin greater than  $45^{\circ}$ . Include worst-case component variations when

determining phase margin. To start the design, a resistor value should be chosen for  $R_1$  from which all other components can be chosen. A good starting value is 24.9 k $\Omega$ .

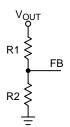

The NCP3170 allows the output of the DC–DC regulator to be adjusted down to  $0.8~\rm V$  via an external resistor divider network. The regulator will maintain  $0.8~\rm V$  at the feedback pin. Thus, if a resistor divider circuit was placed across the feedback pin to  $\rm V_{OUT}$ , the regulator will regulate the output voltage proportional to the resistor divider network in order to maintain  $0.8~\rm V$  at the FB pin.

Figure 46. Feedback Resistor Divider

The relationship between the resistor divider network above and the output voltage is shown in Equation 41:

$$R_2 = R_1 \times \left(\frac{V_{REF}}{V_{OUT} - V_{REF}}\right)$$

(eq. 41)

where:

$\begin{array}{ll} R_1 & = \text{Top resistor divider} \\ R_2 & = \text{Bottom resistor divider} \end{array}$

V<sub>OUT</sub> = Output voltage

$V_{REF}$  = Regulator reference voltage

The most frequently used output voltages and their associated standard  $R_1$  and  $R_2$  values are listed in the table below.

**Table 7. OUTPUT VOLTAGE SETTINGS**

| V <sub>O</sub> (V) | R <sub>1</sub> (kΩ) | R <sub>2</sub> (kΩ) |

|--------------------|---------------------|---------------------|

| 0.8                | 24.9                | Open                |

| 1.0                | 24.9                | 100                 |

| 1.1                | 24.9                | 66.5                |

| 1.2                | 24.9                | 49.9                |

| 1.5                | 24.9                | 28.7                |

| 1.8                | 24.9                | 20                  |

| 2.5                | 24.9                | 11.8                |

| 3.3                | 24.9                | 8.06                |

| 5.0                | 24.9                | 4.64                |

The compensation components for the Pseudo Type III Transconductance Error Amplifier can be calculated using the method described below. The method serves to provide a good starting place for compensation of a power supply. The values can be adjusted in real time using the compensation tool CompCalc

http://www.onsemi.com/pub/Collateral/COMPCALC.ZIP

The first pole to crossover at the desired frequency should be setup at FPO to decrease at  $-20 \, dB$  per decade:

$$F_{PO} = \frac{F_{CROSS}}{G} \rightarrow$$

$$1.354 \text{ kHz} = \frac{50 \text{ kHz}}{36.925} \rightarrow$$

(eq. 42)

where:

$F_{cross}$  = Cross over frequency

$F_{PO}$  = Pole frequency to meet crossover

frequency

G = DC gain of the plant

The crossover combined compensation network can be used to calculate the transconductance output compensation network as follows:

$$C_{C} = \frac{y \times gm}{2 \times \pi \times F_{PO}} \rightarrow$$

$$5.70 \text{ nF} = \frac{0.242 \times 200 \,\mu\text{s}}{2\pi \times 1.354 \text{ kHz}}$$

(eq. 43)

where:

C<sub>C</sub> = Compensation capacitor

$F_{PO}$  = Pole frequency

gm = Transconductance of amplifier

y = Amplitude ratio

$$C_F = \frac{R1 + R2}{2\pi \times (R1 * RF + R2 * RF + R2 * R1) \times F_{cross}} \rightarrow$$

$456 \, pF = \frac{24.9 \, k\Omega \, + \, 7.87 \, k\Omega}{2\pi \, \times \, (24.9 \, k\Omega \, ^{*} 1 \, k\Omega \, + \, 7.87 \, k\Omega \, ^{*} 1 \, k\Omega \, + \, 7.87 \, k\Omega \, ^{*} 24.9 \, k\Omega) \times \, 50 \, kHz}$

where:

C<sub>F</sub> = Compensation pole capacitor

$F_{cross}$  = Cross over frequency

gm = Transconductance of amplifier

$R_1$  = Top resistor divider  $R_2$  = Bottom resistor divider  $R_F$  = Feed through resistor

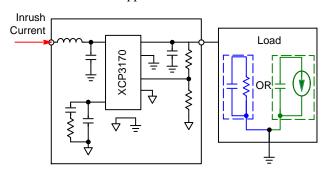

### **Calculating Input Inrush Current**

The input inrush current has two distinct stages: input charging and output charging. The input charging of a buck stage is usually controlled, but there are times when it is not and is limited only by the input RC network, and the output impedance of the upstream power stage. If the upstream power stage is a perfect voltage source and switches on instantaneously, then the input inrush current can be depicted as shown in Figure 47 and calculated as:

$$R_C = \frac{1}{2\pi \times C_C \times F_P} \rightarrow$$

$$2.925 \text{ k}\Omega = \frac{1}{2\pi \times 5.70 \text{ nF} \times 1.354 \text{ kHz}}$$

(eq. 44)

where:

C<sub>C</sub> = Compensation capacitance

C<sub>OUT</sub> = Output capacitance

$F_P$  = Current mode pole frequency

$R_{C}$  = Compensation resistor

$$C_P = \frac{1}{2\pi \times R_C \times F_{ESR}} \rightarrow$$

$$75.2 \text{ pF} = \frac{1}{2\pi \times 2.925 \text{ kQ} \times 723 \text{ kHz}}$$

(eq. 45)

where:

$C_P$  = Compensation pole capacitor  $F_{ESR}$  = Capacitor ESR zero frequency

$R_C$  = Compensation resistor

If the ESR frequency is greater than the switching frequency, a CF compensation capacitor may be needed for stability as the output LC filter is considered high Q and thus will not give the phase boost at the crossover frequency. Further at low duty cycles due to some blanking and filtering of the current signal the current gain of the converter is not constant and the current gain is small. Thus adding CF and RF can give the needed phase boost.

(eq. 46)

Figure 47. Input Charge Inrush Current

$$I_{ICinrush\_PK}1 = \frac{V_{IN}}{CIN_{ESR}}$$

(eq. 47)

$$1.2 \text{ kA} = \frac{12}{0.01}$$

$$I_{ICinrush\_RMS}1 = \frac{V_{IN}}{CIN_{ESR}} \times 0.316 \times \sqrt{\frac{5 \times CIN_{ESR} \times C_{IN}}{t_{DELAY\_TOTAL}}}$$

(eq. 48)

$$12.58 \text{ A} = \frac{12 \text{ V}}{0.01} \times 0.316 \times \sqrt{\frac{5 \times 0.01 \Omega \times 22 \mu F}{1 \text{ ms}}}$$

where:

$\begin{array}{ll} C_{IN} & = \mbox{Output capacitor} \\ CIN_{ESR} & = \mbox{Output capacitor ESR} \\ t_{DELAY\_TOTAL} = \mbox{Total delay interval} \\ V_{IN} & = \mbox{Input Voltage} \\ \end{array}$

Once the t<sub>DELAY\_TOTAL</sub> has expired, the buck converter starts to switch and a second inrush current can be calculated:

$$I_{OCinrush\_RMS} = \frac{\left(C_{OUT} + C_{LOAD}\right) \times V_{OUT}}{t_{SS}} \frac{D}{\sqrt{3}} + I_{CL} \times D \quad \text{(eq. 49)}$$

where:

C<sub>OUT</sub> = Total converter output capacitance

C<sub>LOAD</sub> = Total load capacitance D = Duty ratio of the load I<sub>CL</sub> = Applied load at the output

I<sub>OCinrush\_RMS</sub> = RMS inrush current during start-up

$t_{SS}$  = Soft start interval  $V_{OUT}$  = Output voltage

From the above equation, it is clear that the inrush current is dependent on the type of load that is connected to the output. Two types of load are considered in Figure 48: a resistive load and a stepped current load.

Figure 48. Load Connected to the Output Stage

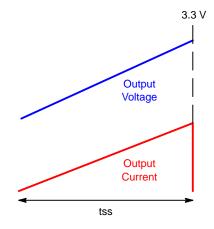

If the load is resistive in nature, the output current will increase with soft start linearly which can be quantified in Equation 50.

$$I_{CLR\_RMS} = \frac{1}{\sqrt{3}} \times \frac{V_{OUT}}{R_{OUT}}$$

$$I_{CR\_PK} = \frac{V_{OUT}}{R_{OUT}}$$

$$(eq. 50)$$

$$191 \text{ mA} = \frac{1}{\sqrt{3}} \times \frac{3.3 \text{ V}}{10 \Omega}$$

$$300 \text{ mA} = \frac{3.3 \text{ V}}{10 \Omega}$$

where:

$\begin{array}{ll} I_{CLR\_RMS} & = RMS \ resistor \ current \\ I_{CR\_PK} & = Peak \ resistor \ current \\ R_{OUT} & = Output \ resistance \\ V_{OUT} & = Output \ voltage \end{array}$

Figure 49. Resistive Load Current

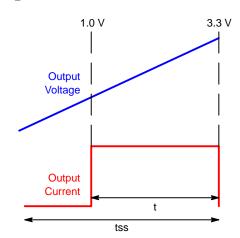

Alternatively, if the output load has an under voltage lockout, turns on at a defined voltage level, and draws a constant current, then the RMS connected load current is:

$$I_{CL1} = \sqrt{\frac{V_{OUT} - V_{OUT\_TO}}{V_{OUT}}} \times I_{OUT}$$

$$(eq. 51)$$

$$492 \text{ mA} = \sqrt{\frac{3.3 \text{ V} - 2.5 \text{ V}}{3.3 \text{ V}}} \times 1 \text{ A}$$

where:

$I_{OUT}$  = Output current  $V_{OUT}$  = Output voltage

$V_{OUT\_TO}$  = Output voltage load turn on

Figure 50. Voltage Enable Load Current

If the inrush current is higher than the steady state input current during max load, then an input fuse should be rated accordingly using I<sup>2</sup>t methodology.

#### THERMAL MANAGEMENT AND LAYOUT

#### Consideration

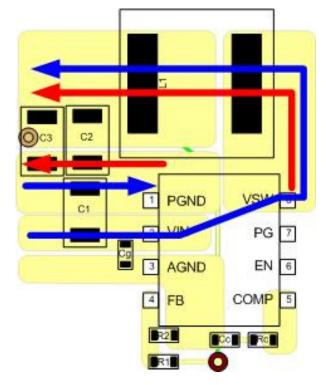

In the NCP3170 buck regulator high pulsing current flows through two loops as shown in the figure below.

Figure 51. Buck Converter Current Paths

The first loop shown in blue activates when the high side switch turns on. When the switch turns on, the edge of the current waveform is provided by the bypass capacitor. The remainder of the current is provided by the input capacitor. Slower currents are provided by the upstream power supply which fills up the input capacitor when the high side switch is off. The current flows through the high side MOSFET and to the output, charging the output capacitors and providing current to the load. The current returns through a PCB ground trace where the output capacitors are connected, the regulator is grounded, and the input capacitors are grounded. The second loop starts from the inductor to the output capacitors and load, and returns through the low side MOSFET. Current flows in the second loop when the low side NMOSFET is on. The designer should note that there are locations where the red line and the blue line overlap; these areas are considered to have DC current. Areas containing a single blue line indicate that AC currents flow and transition very quickly. The key to power supply layout is to focus on the connections where the AC current flows.

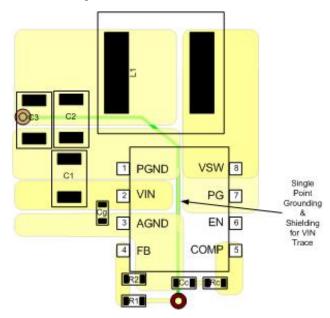

A good rule of thumb is that for every inch of PCB trace, 20 nH of inductance exists. When laying out a PCB, minimizing the AC loop area reduces the noise of the circuit and improves efficiency. A ground plane is strongly recommended to connect the input capacitor, output capacitor, and PGND pin of the NCP3170. Drawing the real high power current flow lines on the recommended layout is

important so the designer can see where the currents are flowing.

Figure 52. Recommended Signal Layout

The NCP3170 is the major source of power dissipation in the system for which the equations above detailed the loss mechanisms. The control portion of the IC power dissipation is determined by the formula below:

$$P_C = I_C \times V_{IN} \qquad (eq. 52)$$

where:

I<sub>CC</sub> = Control circuitry current draw P<sub>C</sub> = Control power dissipation

$V_{IN}$  = Input voltage